CD40192BE CMOS 可預(yù)設(shè) BCD 加/減計(jì)數(shù)器(帶復(fù)位的雙時(shí)鐘)

產(chǎn)品型號(hào):CD40192BE

產(chǎn)品品牌:TI

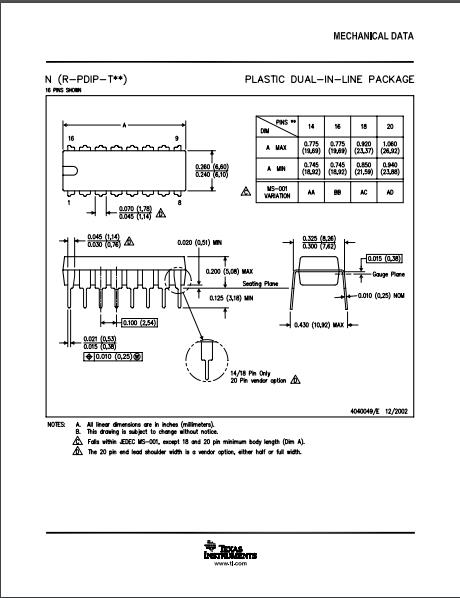

產(chǎn)品封裝:DIP16

產(chǎn)品功能:計(jì)數(shù)器

CD40192BE說明

D40192b 可預(yù)置 BCD 加/減計(jì)數(shù)器和 CD40193B 可預(yù)置二進(jìn)制加/減計(jì)數(shù)器均由 4 個(gè)同步時(shí)鐘��、門控“D”型觸發(fā)器連接為計(jì)數(shù)器�。輸入包括 4 個(gè)單獨(dú)的堵塞線�、一個(gè) PRESET\ENABLE\ 控制、單獨(dú)的 CLOCK UP 和 CLOCK DOWN 信號(hào)以及一個(gè)主 RESET�。提供了四個(gè)緩沖 Q 信號(hào)輸出以及用于多級(jí)計(jì)數(shù)方案的 CARRY\ 和 BORROW\ 輸出。

計(jì)數(shù)器被清零�,因此所有輸出都通過 RESET 線上的高電平處于低電平狀態(tài)。RESET 與時(shí)鐘異步完成����。當(dāng) PRESET\ ENABLE\ 控制為低電平時(shí),每個(gè)輸出都可以與時(shí)鐘異步地單獨(dú)編程到相應(yīng)干擾輸入上的電平�。

如果 CLOCK DOWN 線為高電平,計(jì)數(shù)器會(huì)在 CLOCK UP 信號(hào)的正時(shí)鐘沿向上計(jì)數(shù)一個(gè)計(jì)數(shù)���。如果 CLOCK UP 線為高電平,計(jì)數(shù)器會(huì)在 CLOCK DOWN 信號(hào)的正時(shí)鐘邊沿進(jìn)行遞減計(jì)數(shù)���。

CARRY\ 和 BORROW\ 信號(hào)為高電平����,計(jì)數(shù)器正在向上或向下計(jì)數(shù)����。在向上計(jì)數(shù)模式下,計(jì)數(shù)器達(dá)到其最大計(jì)數(shù)后的一個(gè)半時(shí)鐘周期�����,CARRY\ 信號(hào)變低����。BORROW\ 信號(hào)在倒計(jì)時(shí)模式下計(jì)數(shù)器達(dá)到其最小計(jì)數(shù)后的一個(gè)半時(shí)鐘周期變低。通過將 BORROW\ 和 CARRY\ 輸出分別連接到后續(xù)計(jì)數(shù)器包的 CLOCK DOWN 和 CLOCK UP 輸入��,無需額外的外部電路即可輕松實(shí)現(xiàn)多個(gè)包的級(jí)聯(lián)��。

CD40192B 和 CD40193B 型采用 16 引腳密封雙列直插陶瓷封裝(F3A 后綴)���、16 引腳雙列直插塑料封裝(E 后綴)�、16 引腳小外形封裝(NSR 后綴)和 16 引腳薄型收縮小外形封裝(PW 和 PWR 后綴)。

CD40192BE特征

●用于向上或向下計(jì)數(shù)的單獨(dú)時(shí)鐘線

●用于級(jí)聯(lián)的同步高速進(jìn)位和借位傳播延遲

●異步復(fù)位和預(yù)設(shè)能力

●中速運(yùn)行–f CL = 8MHz(典型值)@ 10 V

●5V���、10V 和 15V 參數(shù)額定值

●標(biāo)準(zhǔn)化����、對(duì)稱的輸出特性

●100% 測試了 20 V 下的靜態(tài)電流

●在整個(gè)封裝溫度范圍內(nèi) 18 V 時(shí)的最大輸入電流為 1 µA�;在 18V 和 25°C 時(shí)為 100nA

●噪聲容限(整個(gè)封裝溫度范圍)=

1 V at V DD = 5 V

2 V at V DD = 10 V

2.5 V at V DD = 15 V

●符合 JEDEC 暫定標(biāo)準(zhǔn) No. 13B�����,“'B' 系列 CMOS 器件描述的標(biāo)準(zhǔn)規(guī)范”的所有要求