TMS320DM8168CCYG2 達(dá)芬奇數(shù)字媒體處理器

產(chǎn)品型號(hào):TMS320DM8168CCYG2

產(chǎn)品品牌:TI

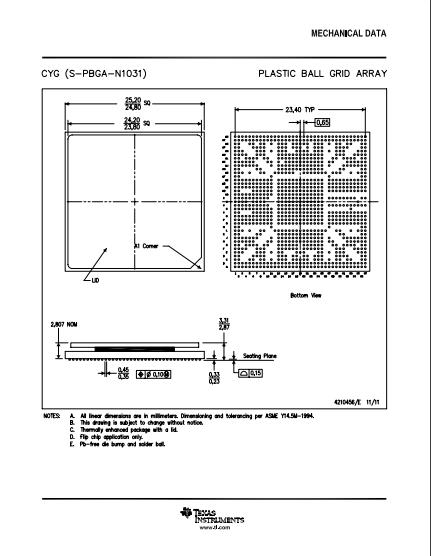

產(chǎn)品封裝:BGA

產(chǎn)品功能:處理器

TMS320DM8168CCYG2說(shuō)明

DM816x 達(dá)芬奇視頻處理器是一個(gè)高度集成的可編程平臺(tái)���,它利用 TI 的達(dá)芬奇技術(shù)來(lái)滿足以下應(yīng)用的處理需求:視頻編碼�、解碼�����、轉(zhuǎn)碼和轉(zhuǎn)碼率��;視頻安全;視頻會(huì)議; 視頻基礎(chǔ)設(shè)施;媒體服務(wù)器���;和數(shù)字標(biāo)牌�。

該器件使原始設(shè)備制造商 (OEM) 和原始設(shè)計(jì)制造商 (ODM) 能夠通過(guò)完全集成的混合處理器解決方案的最大靈活性���,快速將具有強(qiáng)大操作系統(tǒng)支持、豐富用戶界面和高處理性能的設(shè)備推向市場(chǎng)����。該器件將可編程視頻和音頻處理與高度集成的外設(shè)集相結(jié)合。

該器件的關(guān)鍵是多達(dá)三個(gè)高清視頻和成像協(xié)處理器 (HDVICP2)��。每個(gè)協(xié)處理器可以執(zhí)行單個(gè) 1080p60 H.264 編碼或解碼或多個(gè)較低分辨率或幀速率的編碼和解碼�。多通道 HD-to-HD 或 HD-to-SD 轉(zhuǎn)碼和多重編碼也是可能的����。TMS320DM816x 器件能夠同時(shí)處理 1080p60 流,是滿足當(dāng)今苛刻的高清視頻應(yīng)用要求的強(qiáng)大解決方案�。

可編程性由具有 NEON 擴(kuò)展的 ARM Cortex-A8 RISC CPU、TI C674x VLIW 浮點(diǎn) DSP 內(nèi)核以及高清視頻和成像協(xié)處理器提供。ARM 處理器讓開(kāi)發(fā)人員可以將控制功能與在 DSP 和協(xié)處理器上編程的音頻和視頻算法分開(kāi)��,從而降低系統(tǒng)軟件的復(fù)雜性��。帶有 NEON 浮點(diǎn)擴(kuò)展的 ARM Cortex-A8 32 位 RISC 處理器包括: 32KB 指令緩存���;32KB數(shù)據(jù)緩存�����;256KB 二級(jí)緩存;48KB 的公共 ROM 和 64KB 的 RAM���。

豐富的外圍設(shè)備集提供了控制外部外圍設(shè)備和與外部處理器通信的能力。有關(guān)每個(gè)外設(shè)的詳細(xì)信息��,請(qǐng)參閱本文檔中的相關(guān)部分和相關(guān)的外設(shè)參考指南��。外圍設(shè)備包括: 高清視頻處理子系統(tǒng) (HDVPSS)���,提供同時(shí)輸出高清和標(biāo)清模擬視頻以及雙高清視頻輸入����;最多兩個(gè)具有 GMII 和 MDIO 接口的千兆以太網(wǎng) MAC(10 Mbps��、100�����、Mbps�����、1000 Mbps)���;兩個(gè)帶有集成 2.0 PHY 的 USB 端口;PCIe 端口 x2 通道 GEN2 兼容接口��,允許設(shè)備充當(dāng) PCIe 根聯(lián)合體或設(shè)備端點(diǎn);1個(gè)6通道McASP音頻串口(帶DIT模式)�;兩個(gè)雙通道 McASP 音頻串口(帶 DIT 模式)����;一個(gè) McBSP 多通道緩沖串行端口����;三個(gè)支持 IrDA 和 CIR 的 UART;SPI串行接口����;SD和SDIO串行接口��;兩個(gè)我2C主從接口��;多達(dá) 64 個(gè) GPIO 引腳����;七個(gè) 32 位定時(shí)器;系統(tǒng)看門狗定時(shí)器���;雙 DDR2 和 DDR3 SDRAM 接口��;靈活的 8 位和 16 位異步存儲(chǔ)器接口����;以及多達(dá)兩個(gè) SATA 接口,用于在兩個(gè)或更多磁盤驅(qū)動(dòng)器上使用端口倍增器進(jìn)行外部存儲(chǔ)�����。

該器件還包括一個(gè) SGX530 3D 圖形引擎(僅在 TMS320DM8168 器件上可用)���,以實(shí)現(xiàn)復(fù)雜的 GUI 和引人注目的用戶界面和交互���。此外,該器件還具有一整套適用于 ARM 和 DSP 的開(kāi)發(fā)工具���,包括 C 編譯器�、用于簡(jiǎn)化編程和調(diào)度的 DSP 匯編優(yōu)化器�,以及用于查看源代碼執(zhí)行的 Microsoft Windows 調(diào)試器接口�����。

C674x DSP 內(nèi)核是 TMS320C6000 DSP 平臺(tái)中的高性能浮點(diǎn) DSP 系列。C674x 浮點(diǎn) DSP 處理器使用 32KB 的 L1 程序存儲(chǔ)器和 32KB 的 L1 數(shù)據(jù)存儲(chǔ)器��。高達(dá) 32KB 的 L1P 可配置為程序緩存�。剩下的是不可緩存的無(wú)等待狀態(tài)程序存儲(chǔ)器。高達(dá) 32KB 的 L1D 可配置為數(shù)據(jù)緩存��。剩下的是不可緩存的無(wú)等待狀態(tài)數(shù)據(jù)存儲(chǔ)器���。DSP 具有 256KB 的 L2 RAM,可定義為 SRAM����、L2 高速緩存或兩者的組合。所有 C674x L3 和片外存儲(chǔ)器訪問(wèn)均通過(guò)系統(tǒng) MMU 進(jìn)行路由�����。

該器件封裝采用 Via Channel 技術(shù)進(jìn)行了專門設(shè)計(jì)�����。該技術(shù)允許在這種 0.65 毫米間距封裝中使用 0.8 毫米間距 PCB 特征尺寸�����,并顯著降低 PCB 成本�����。由于 Via Channel BGA 技術(shù)提高了層效率��,Via Channel 技術(shù)還允許僅在兩個(gè)信號(hào)層中進(jìn)行 PCB 布線。

TMS320DM8168CCYG2特征

●高性能達(dá)芬奇數(shù)字媒體處理器

●ARM ® Cortex-A8 RISC 處理器

●高達(dá) 1.20 GHz

●C674x VLIW DSP

●高達(dá) 1 GHz

●高達(dá) 8000 MIPS 和 6000 MFLOPS

●與 C67x+ 和 C64x+ 完全軟件兼容

●ARM Cortex-A8 內(nèi)核

●ARMv7 架構(gòu)

●有序�、雙問(wèn)題、超標(biāo)量處理器內(nèi)核

●NEON多媒體架構(gòu)

●支持整數(shù)和浮點(diǎn)數(shù)(符合 VFPv3-IEEE754)

●Jazelle RCT 執(zhí)行環(huán)境

●ARM Cortex-A8 內(nèi)存架構(gòu)

●32 KB 指令和數(shù)據(jù)緩存

●256 KB 二級(jí)緩存

●64 KB RAM�����,48 KB 引導(dǎo) ROM

●TMS320C674x 浮點(diǎn) VLIW DSP

●64 個(gè)通用寄存器(32 位)

●六個(gè) ALU(32 位和 40 位)功能單元

●支持 32 位整數(shù)����、SP(IEEE 單精度�、32 位)和 DP(IEEE 雙精度��、64 位)浮點(diǎn)

●每個(gè)時(shí)鐘最多支持四個(gè) SP 添加和每?jī)蓚€(gè)時(shí)鐘添加四個(gè) DP

●每個(gè)周期最多支持兩個(gè)浮點(diǎn)(SP 或 DP)近似倒數(shù)或平方根運(yùn)算

●兩個(gè)乘法功能單元

●混合精度 IEEE 浮點(diǎn)乘法支持高達(dá):

●2 SP x SP → SP 每時(shí)鐘

●2 SP x SP → DP 每?jī)蓚€(gè)時(shí)鐘

●2 SP x DP → DP 每三個(gè)時(shí)鐘

●2 DP x DP → DP 每四個(gè)時(shí)鐘

●定點(diǎn)乘法支持兩個(gè) 32 x 32 乘法���、四個(gè) 16 x 16 位乘法(包括復(fù)數(shù)乘法)或每個(gè)時(shí)鐘周期八個(gè) 8 x 8 位乘法

●C674x 兩級(jí)內(nèi)存架構(gòu)

●32 KB L1P 和 L1D RAM 和高速緩存

●256 KB L2 統(tǒng)一映射 RAM 和緩存

●系統(tǒng)內(nèi)存管理單元(系統(tǒng) MMU)

●將 C674x DSP 和 EMDA TCB 存儲(chǔ)器訪問(wèn)映射到系統(tǒng)地址

●512KB 片上內(nèi)存控制器 (OCMC) RAM

●媒體控制器

●管理 HDVPSS 和 HDVICP2 模塊

●多達(dá)三個(gè)可編程高清視頻圖像協(xié)處理 (HDVICP2) 引擎

●編碼���、解碼����、轉(zhuǎn)碼操作

●H.264��、MPEG-2、VC-1�、MPEG-4 SP 和 ASP

●SGX530 3D 圖形引擎(僅在 DM8168 設(shè)備上可用)

●每秒提供多達(dá) 30 個(gè) MTriangles

●通用可擴(kuò)展著色器引擎

●Direct3D Mobile�����、OpenGL ES 1.1 和 2.0、OpenVG 1.1�、OpenMax API 支持

●高級(jí)幾何 DMA 驅(qū)動(dòng)操作

●可編程 HQ 圖像抗鋸齒

●字節(jié)序

●ARM�、DSP 指令和數(shù)據(jù) – Little Endian

●高清視頻處理子系統(tǒng) (HDVPSS)

●兩個(gè) 165-MHz 高清視頻采集通道

●一個(gè) 16 位或 24 位和一個(gè) 16 位通道

●每個(gè)通道可拆分為雙 8 位捕獲通道

●兩個(gè) 165-MHz 高清視頻顯示通道

●一個(gè) 16 位、24 位��、30 位通道和一個(gè) 16 位通道

●同時(shí)標(biāo)清和高清模擬輸出

●具有高達(dá) 165MHz 像素時(shí)鐘的 HDCP 的 PHY 數(shù)字 HDMI 1.3 發(fā)送器

●三個(gè)圖形層

●雙 32 位 DDR2 和 DDR3 SDRAM 接口

●最高支持 DDR2-800 和 DDR3-1600

●總共多達(dá) 8 個(gè) x8 設(shè)備

●2GB 總地址空間

●動(dòng)態(tài)內(nèi)存管理器 (DMM)

●可編程多區(qū)域內(nèi)存映射和交錯(cuò)

●實(shí)現(xiàn)高效的 2D 塊訪問(wèn)

●支持 0°�、90°����、180° 或 270° 方向和鏡像的平鋪對(duì)象

●優(yōu)化交錯(cuò)訪問(wèn)

●一個(gè) PCI Express (PCIe) 2.0 帶有集成 PHY 的端口

●具有 1 或 2 個(gè)通道的單端口��,每秒 5.0 GT

●可配置為根聯(lián)合體或端點(diǎn)

●具有集成 PHY 的串行 ATA (SATA) 3.0 Gbps 控制器

●兩個(gè)硬盤驅(qū)動(dòng)器的直接接口

●來(lái)自多達(dá) 32 個(gè)條目的硬件輔助本機(jī)命令隊(duì)列 (NCQ)

●支持端口倍增器和基于命令的切換

●兩個(gè) 10 Mbps、100 Mbps 和 1000 Mbps 以太網(wǎng) MAC (EMAC)

●符合 IEEE 802.3(僅限 3.3-VI/O)

●MII 和 GMII 媒體獨(dú)立接口

●管理數(shù)據(jù) I/O (MDIO) 模塊

●具有集成 PHY 的雙 USB 2.0 端口

●USB 2.0 高速和全速客戶端

●USB 2.0 高速���、全速和低速主機(jī)

●支持端點(diǎn) 0-15

●通用內(nèi)存控制器 (GPMC)

●8 位和 16 位復(fù)用地址和數(shù)據(jù)總線

●多達(dá) 6 個(gè)片選,每個(gè)片選引腳具有多達(dá) 256-MB 的地址空間

●與 NOR 閃存���、NAND 閃存(帶 BCH 和漢明錯(cuò)誤代碼檢測(cè))�����、SRAM 和偽 SRAM 的無(wú)膠接口

●GPMC 之外的錯(cuò)誤定位器模塊 (ELM) 可為 NAND 提供高達(dá) 16 位和 512 字節(jié)的硬件 ECC

●FPGA���、CPLD、ASIC 接口的靈活異步協(xié)議控制

●增強(qiáng)型直接內(nèi)存訪問(wèn) (EDMA) 控制器

●四個(gè)傳輸控制器

●64 個(gè)獨(dú)立 DMA 通道和 8 個(gè)快速 DMA (QDMA) 通道

●七個(gè) 32 位通用定時(shí)器

●一個(gè)系統(tǒng)看門狗定時(shí)器

●三個(gè)可配置的 UART���、IrDA 和 CIR 模塊

●帶有調(diào)制解調(diào)器控制信號(hào)的 UART0

●支持高達(dá) 3.6864 Mbps 的 UART

●SIR�、MIR�、FIR (4.0 MBAUD) 和 CIR

●一個(gè)具有四個(gè)芯片選擇的 40MHz 串行外設(shè)接口 (SPI)

●SD 和 SDIO 串行接口(1 位和 4 位)

●雙內(nèi)部集成電路(I 2 C 總線)端口

●三個(gè)多通道音頻串行端口 (McASP)

●一個(gè)六串行器發(fā)送和接收端口

●兩個(gè)雙串行器發(fā)送和接收端口

●支持 SDIF 和 PDIF(所有端口)的 DIT

●多通道緩沖串行端口 (McBSP)

●發(fā)送和接收時(shí)鐘高達(dá) 48 MHz

●兩個(gè)時(shí)鐘區(qū)域和兩個(gè)串行數(shù)據(jù)引腳

●支持 TDM、I2S 和類似格式

●實(shí)時(shí)時(shí)鐘 (RTC)

●一次性或周期性中斷生成

●多達(dá) 64 個(gè)通用 I/O (GPIO) 引腳

●片上 ARM ROM 引導(dǎo)加載程序 (RBL)

●電源�����、復(fù)位和時(shí)鐘管理

●SmartReflex 技術(shù)(2 級(jí))

●七個(gè)獨(dú)立的核心電源域

●子系統(tǒng)和外設(shè)的時(shí)鐘啟用和禁用控制

●IEEE 1149.1 (JTAG) 和 IEEE 1149.7 (cJTAG) 兼容

●Via Channel 技術(shù)支持使用

●0.8-mm 設(shè)計(jì)規(guī)則

●40 納米 CMOS 技術(shù)

●3.3V 單端 LVCMOS I/O(1.5V 的 DDR3、1.8V 的 DDR2 和 1.8V 的 DEV_CLKIN 除外)

封裝圖